摘要: 随着5G、人工智能(AI)、车用电子、物联网(IoT)、高效运算(HPC)等半导体新应用领域百花齐放,晶圆制造先进制程在台积电的引领之下走向7、5、3奈米,但随着摩尔定律逐渐逼近物理极限,让摩尔定律延寿的良方之一为先进封装技术,包括扇出型晶圆级封装(FOWLP)、2.5D/3D IC封装,更进一步进入更能够异质整合的3D晶圆堆栈封装。

随着5G、人工智能(AI)、车用电子、物联网(IoT)、高效运算(HPC)等半导体新应用领域百花齐放,晶圆制造先进制程在台积电的引领之下走向7、5、3奈米,但随着摩尔定律逐渐逼近物理极限,让摩尔定律延寿的良方之一为先进封装技术,包括扇出型晶圆级封装(FOWLP)、2.5D/3D IC封装,更进一步进入更能够异质整合的3D晶圆堆栈封装。

而各类新兴应用推动半导体异质整合蔚为趋势,软、硬件大厂如苹果(Apple)、Google、亚马逊(Amazon)等巨人纷纷开始自行设计芯片以追求差异化特色,也使得封测厂争取系统大厂订单成为兵家必争之地。

台积电、三星封装技术比较

加上5G通信世代将有更多异质整合不同元件的需求,都持续带动系统级封装(SiP)需求大开,也进一步使得前段晶圆测试(CP),以及更后段的系统级测试(SLT)重要性随之提升,将成为走过2018年,迎向2019年IC封测产业的主要发展方向。

力抗三星、英特尔 台积电跨足先进封装脚步未停歇

台积电为了全力拉开与三星电子(Samsung Electronics)、英特尔(Intel)差距,除了揭露第四代CoWoS(Chip on Wafer on Substrate)封装预计2019年量产,因应AI世代HPC芯片需求,台积电第五代CoWoS封装制程2020年将问世。

尽管市场上不乏台积电与专业委外封测代工(OSAT)厂竞争说法,但事实上,台积电向来强调跨足封装为晶圆段(Wafer-Level)的延伸,其用意也不是要与OSAT竞争。

台积电CoWoS封装制程主要锁定核心等级的HPC芯片,并已提供美系GPU、FPGA客户从晶圆制造绑定先进封装的服务,加上SoIC封装技术齐备,先进封装技术WLSI(Wafer-Level-System-Integration)平台阵容更加坚强,也更够协助芯片业者能够享有先进制程与先进封装的一条龙服务,进一步在新世代中确保强大的算力。

台积电第四代CoWoS能够提供现行约26mmx32mm倍缩光罩(约830~850平方公厘)的2倍尺寸,来到约1,700平方公厘。预计2020年推出第五代CoWoS封装,倍缩光罩尺寸更来到现行的3倍,约2,500平方公厘,可乘载更多不同的Chip、更大的Die Size、更多的接脚数。

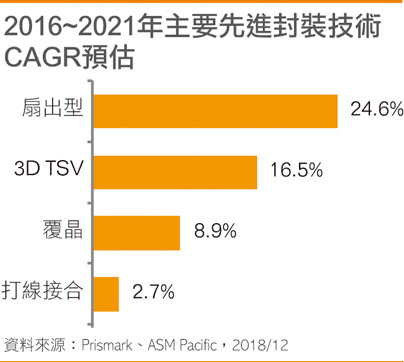

2016~2021年主要先进封装技术CAGR预估

台积电提出的先进封装技术WLSI平台,已经纳入相较InFO、CoWoS更为前段的SoIC、3D Wafer-on-Wafer(WoW)堆栈封装。SoIC制程,主要针对10奈米等晶圆制造先进制程进行「晶圆对晶圆」的接合技术,可把不同芯片异质整合,由于IP都已经认证,可降低客户成本,达到高效能、低功耗的需求,也近似于系统级封装(SiP)概念。

台积电WLSI平台包括既有的CoWoS封装、InFO封装,以及针对PM-IC等较低阶芯片的扇入型晶圆级封装(Fan-In WLP)。其中,CoWoS协助台积电拿下NVIDIA、超微(AMD)、Google、赛灵思(Xilinx)、海思等高阶HPC芯片订单。InFO则主要应用于行动装置AP,巩固苹果AP晶圆代工订单,随着InFO陆续推出衍生型版本,预计将持续切入网通相关领域,以及即将来到的5G世代通讯芯片。

值得一提的是,继台积电SoIC等新概念封装技术发布不久,英特尔也发表新款3D封装的「Foveros」技术,同样看重整合逻辑IC与存储器的半导体异质整合大势,应用领域锁定高效能逻辑芯片、CPU、GPU、AI处理器等。

在半导体制程微缩逐渐逼近物理极限下,举凡台积电的SoIC、英特尔的Foveros,其实概念上都偏向了SiP,重点为把不同制程的芯片异质整合,英特尔强调将把各类存储器、IP模块、I/O元件整合,产品可分解成更小的「chiplet」。

其中I/O,SRAM和电源传输电路可以建入底层芯片(base die)当中,高效能逻辑芯片则堆栈于其上。英特尔预计将自2019年下半开始使用Foveros推出一系列产品,首款Foveros产品将结合高效能10奈米运算堆栈小芯片和低功耗22FFL底层芯片,力求轻薄短小、高效能、低功耗。

FOPLP韩厂、力成抢进 日月光投控静观其变

相较于成本偏高的晶圆级扇出封装,业界也在思考扇出型封装能否有更具成本效益的制程。尽管台系封测业者日月光投控、力成都高喊FOPLP商机,然目前看来,三星集团旗下三星电机(Semco)仍是最敢投资FOPLP技术的业者,且三星电机已量产可与InFO、CoWoS封装分庭抗礼的FOPLP-PoP与I-Cube 2.5D先进封装技术。

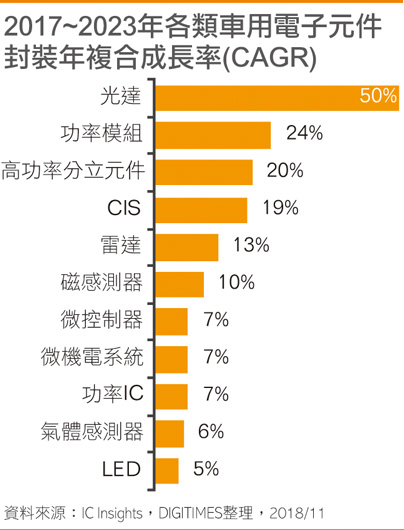

2017~2023年各类车用电子元件封装年复合成长率

三星电机FOPLP最初用来生产电源管理芯片(PM-IC),但2018年已开始导入量产穿戴式装置的AP芯片,供应自家穿戴式装置新品Galaxy Watch使用,预计2019年全面跨入异质整合、晶圆堆栈的3D SiP系统级封装。

FOPLP仍面临不小的挑战,以目前FOPLP刚起步的状况来看,经济规模将是技术普及的最大挑战,在初期良率还不够好的状态下,FOPLP产能要达到理想的成本优势,短期内恐不易达成。

FOPLP精细度要提升不容易,这亦是三星先切入相对低阶的穿戴式装置AP,目前尚无法取得高阶智能型手机等级的客户订单,面对未来高效运算时代,包括AP、AI芯片、GPU、ASIC或FPGA等高阶芯片,恐无法使用现行的FOPLP设备量产,况且FOPLP同样有翘曲(warpage)等问题待解决。

FOPLP制程设备投资风险大亦是一大考量,由于FOPLP无法沿用既有面板或晶圆制造设备,多数业者必须以新制程制作设备,机台的成本相当高,若是经济规模不够大,量能无法支撑成本,投资回收将有相当的难度。

台系OSAT业者中力成大力宣布投入FOPLP新产能。力成于2018年9月25日举行竹科三厂动土典礼,由力成董事长蔡笃恭亲自主持,FOPLP新厂估计投资的总金额将达新台币500亿元,工程预计于2020年上半完成,并将于2020年下半开始装机量产。

力成于2004年就以TSV(硅穿孔)的3D IC封装技术为基础,并且开始投入发展大尺寸FOPLP封测,2016年底在竹科装置完成全球第一条FOPLP研发与小量生产的生产线,设备投资已经超过1亿美元。

FOPLP可降低封装厚度、增加导线密度、提升产品电性、面板大工作平台可提高生产效率、晶体管微型将具备开发时间短与成本低等优势。面板级扇出型封装技术更将可提供最佳的系统级封装(SiP)解决方案。

OSAT龙头日月光也已经在FOPLP技术上齐备,估计2019年中以后至2020年都有机会视客户需求量产。日月光在面板级扇出封装规格上力求统一,订出300x300mm、600x600mm面板尺寸规格,针对各类植基于扇出型封装的高阶封装制程都可以支援。

举凡日月光所提出针对中高阶服务器、资料中心、FPGA芯片、GPU的FOCoS(Fan-Out Chip-on-Substrate)封装,以及适用于通讯产品、网通处理器的FOPoP(Fan-Out Package-on-Package)封装、甚至适用于量能庞大的RF-IC、PM-IC的eWLB封装制程,日月光FOPLP产能都将可以支援,对于大、中、小型芯片封装需求可说通吃。

系统厂订单重要性增 EMS模式抢SiP、SLT商机

全球产业竞争局势丕变,龙头软、硬件业者如苹果、亚马逊、Google甚至Tesla等纷纷朝自行设计芯片方向迈进,这也使得封测厂必须更进一步巩固系统厂生意订单。而系统厂欲自行设计芯片的关键,也无非希望能够生产具更具差异化、具有特色的芯片,进一步在竞争激烈的市场中脱颖而出。

日月光投控提出新3C概念,包括整合collect、compute、connect,将是未来封测产业广大机会,应用层面包括智慧生活、到自主生活,半导体都会是基本需求。从AI发展的角度来看,不只是资料中心(Data Center),边缘运算(Edge-computing)也是重要关节。

不管是手表、智能型手机等等,这些边缘运算需求都需要SiP模块助攻。若能够把不同芯片整合封装,形成新的微系统扩大市场,也可增加更多系统投资,形成正向循环。

各类微系统中的传感器背后还有系统单晶片(SoC),在HPC趋势下要求的功能越来越高、越来越多,业界更会思考要怎样把不同芯片放在同一系统上,如何把不同功能的不同芯片封装的更短小,这些设计都可用委托OSAT大厂以SiP封装来解决,令独特性、差异化提升。

事实上,举凡台积电、英特尔提出的新款3D封装,强调的都是逻辑芯片整合存储器等SiP的异质整合特色,这也意味着国际大厂追求的不再是逼近摩尔定律极限的制程微缩,而是异质整合。而各类SiP封装需求的窜出,业界思考是否有机会进一步放大产量、降低成本外,SiP也同样会出现更多来自于半导体测试的挑战。

由于先进制程与高阶芯片的复杂性与成本不可同日而语,最前段的晶圆测试(CP)必须更为精准,关键在于晶圆测试探针卡(Probe Card)的设计,而最后段的系统级测试,则使得测试业者必须进一步把原本EMS系统代工厂行之已久的测试模式移到半导体领域,这也将横跨IC、自动化设备、SLT等不同领域。

5G、AIoT等应用,因应异质整合需求的SiP封装模块势必有更大量能需求,进入大批量测试时,封测业者不仅藉由系统级测试得知SiP模块堪用与否,更希望能够找出异质整合的元件中,哪一部分出现问题。

随着5G芯片的复杂度以及半导体制造先进制程成本增加,测试端的重要性自然也不可同日而语。能够熟悉自动化测试设备(ATE)、SLT、IC等能够跨领域沟通的人才,目前亦相对缺乏。OSAT厂与测试设备厂的角色,事实上也更往类似于EMS厂的方向靠拢,未来如何在SiP时代建立起有效率的SLT产业链,也将是重要课题。

作者:何致中

社群二维码

关注“华强商城“微信公众号

Copyright 2010-2023 hqbuy.com,Inc.All right reserved. 服务热线:400-830-6691 粤ICP备05106676号 经营许可证:粤B2-20210308